Interesting interview by Nikkei Business with Mr. Shigeki Ishizuka, a former Sony digital camera developer.…

Industry News: Sony Develops World’s First Stacked CMOS Sensor With 2-Layer Transistor Pixel

Sony announced the development of a new image sensor with 2-Layer transistor pixels.

Sony press release:

Sony Develops World’s First*1 Stacked CMOS Image Sensor Technology

with 2-Layer Transistor Pixel

Widens Dynamic Range and Reduces Noise by Approximately Doubling*2 Saturation Signal Level*3

*1: As of announcement on December 16, 2021.

*2: Based on comparison, on a one square μm equivalent basis, between existing image sensor and the new technology applied to Sony’s back-illuminated CMOS image sensor; as of announcement on December 16, 2021.

*3: A single pixel’s maximum electron storage capacity.

Sony Semiconductor Solutions Corporation (“Sony”) has succeeded in developing the world’s first*1 stacked CMOS image sensor technology with 2-Layer Transistor Pixel. Whereas conventional CMOS image sensors’ photodiodes and pixel transistors occupy the same substrate, Sony’s new technology separates photodiodes and pixel transistors on different substrate layers. This new architecture approximately doubles*2 saturation signal level*3 relative to conventional image sensors, widens dynamic range and reduces noise, thereby substantially improving imaging properties. The new technology’s pixel structure will enable pixels to maintain or improve their existing properties at not only current but also smaller pixel sizes.

Sony announced this breakthrough at the IEEE International Electron Devices Meeting that started on Saturday, December 11, 2021.

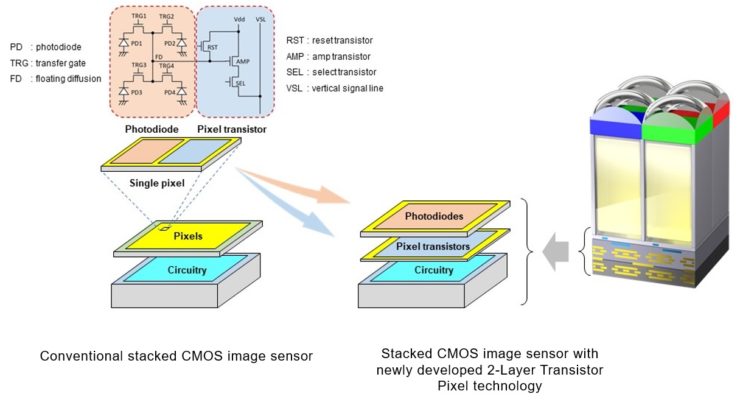

Stacked CMOS image sensor architectures

A stacked CMOS image sensor adopts a stacked structure consisting of a pixel chip made up of back-illuminated pixels stacked atop a logic chip where signal processing circuits are formed. Within the pixel chip, photodiodes for converting light to electrical signals, and pixel transistors for controlling the signals are situated alongside each other on the same layer. Increasing saturation signal level within form-factor constraints plays an important role in realizing high image quality with wide dynamic range.

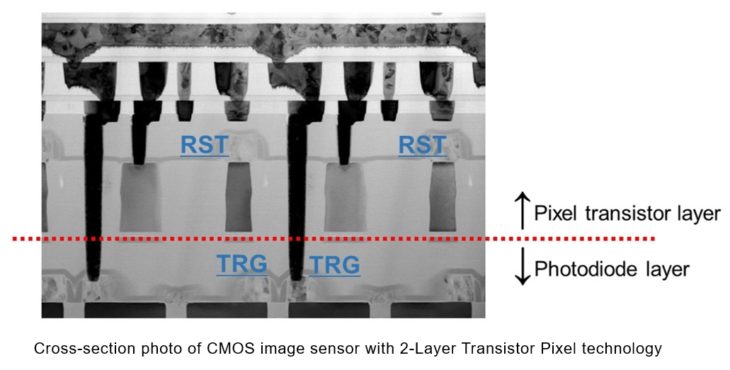

Sony’s new architecture is an advancement in stacked CMOS image sensor technology. Using its proprietary stacking technology, Sony packaged the photodiodes and pixel transistors on separate substrates stacked one atop the other.

In conventional stacked CMOS image sensors, by contrast, the photodiodes and pixel transistors sit alongside each other on the same substrate. The new stacking technology enables adoption of architectures that allow the photodiode and pixel transistor layers to each be optimized, thereby approximately doubling saturation signal level relative to conventional image sensors and, in turn, widening dynamic range.

Additionally, because pixel transistors other than transfer gates (TRG), including reset transistors (RST), select transistors (SEL) and amp transistors (AMP), occupy a photodiode-free layer, the amp transistors can be increased in size. By increasing amp transistor size, Sony succeeded in substantially reducing the noise to which nighttime and other dark-location images are prone.

The widened dynamic range and noise reduction available from this new technology will prevent underexposure and overexposure in settings with a combination of bright and dim illumination (e.g., backlit settings) and enable high-quality, low-noise images even in low-light (e.g., indoor, nighttime) settings.

Sony will contribute to the realization of increasingly high-quality imaging such as smartphone photographs with its 2-Layer Transistor Pixel technology.

[via Sony Alpha Rumors]